Florida Sun Shines Light on Electronic Packaging Trends

3D packages, fan-out WLPs, and the migration to copper wire bonding highlighted ECTC.

A thousand people gathered at the Electronics Components and Technology Conference (ECTC) in Orlando, FL, last month to discuss the latest trends in electronics packaging and assembly.

Among the hot topics were 3D packages, including package-on-package (PoP) and through silicon via (TSV) interconnect. Fan-out wafer-level packages (WLPs), copper pillar bumping, new substrate developments such as silicon and glass interposers, embedded components, LEDs, optoelectronics, and copper wire bonding were topics of great discussion. Many new material developments, especially related to underfill were presented.

Several presentations focused on advances in PoP technology. Companies including Amkor, Endicott Interconnect, Micron, Powertech Technology, and STATS ChipPAC discussed advances in PoP technology that might enable continued double-digit growth.

3D TSV presentations accounted for at least 76 of the 342 papers this year, compared with 50 of the 323 papers presented at last year’s conference. Aspects of the 3D TSV process discussed included new material developments and process improvements, indicating steady progress over the year. While there is still a lot of PowerPoint engineering, it is clear that some of the tough areas such as wafer handling and thinning are being addressed. Many joint papers were published by IBM and its various development partners, research organizations such as IMEC (Belgium), ITRI (Taiwan), IME/A*STAR (Singapore), and multiple Fraunhofer Institutes (Germany).

Sprinkled throughout the TSV sessions were several papers from Xilinx detailing plans for silicon interposers with TSVs fabricated by TSMC. In addition to TSMC, several other groups discussed research on silicon and glass interposers, including Shinko Electric, Taiyo Yuden, Asahi Glass, Zeon, STMicroelectronics, Georgia Tech, and the Fraunhofer IZM.

Several presentations for a variety of international research organizations and companies, including CEA-LETI, Fraunhofer IWM, IBM, IME/A*STAR, IMEC, ITRI, Samsung, TI and TSMC, focused on the development of micro bumps for true 3D TSV, as well as for interposers. A session on the last day of the conference focused on 3D package reliability. In the session, researchers from the Fraunhofer IWM detailed research results from their work in electro- and thermo-migration in micro bump interconnects for 3D integration.

Fan-out WLPs. STATS ChipPAC, STMicroelectronics, and Intel reported on research in combining eWLB fan-out WLP technology with TSV and integrated passive device technology to achieve new levels of heterogeneous integration. Several companies reported on process improvements in fan-out WLPs. In a combined effort with the equipment supplier Ultratech, Infineon’s wireless group (now part of Intel) discussed new lithography techniques to reduce alignment errors from die placement. The newly formed Renesas, which now includes NEC, detailed its fan-out process.

While fan-out WLPs are the latest buzzword, several companies, including Qualcomm, discussed improvements in WLPs that will help extend the technology to a broader range of devices.

Wire bond and flip chip. With the price of gold surpassing $1,500/troy oz., the shift from gold to copper wire bonding continues for a variety of packages. Several papers considered the use of Pd-coated copper wire. Palladium coating provides for oxidation protection, resulting in a longer shelf life. While there are still some technical challenges with the shift to copper, much progress is being made, and the price of gold remains a major driver.

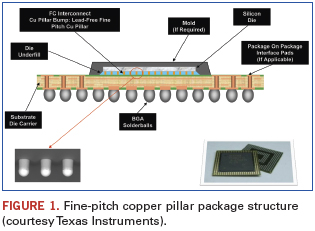

An increasing number of devices are transitioning from wire bond to flip chip. Companies are looking at finer pitch bumps and Pb-free solutions that will work with the new ultra low-k dielectric materials used on the device. Many companies are interested in copper pillar for fine-pitch applications as a way to reduce cost, including the cost of the substrate. Amkor and Texas Instruments revealed more of the joint development work that has enabled adoption of copper pillar at TI. STATS ChipPAC has also championed the combined development of copper pillar and low-cost substrates – especially when combined with molded underfills.

Planning for next year’s ECTC is already underway for San Diego. Another record crowd of international electronics industry participants can be expected to engage in discussions on the latest technologies. Abstract submissions are due in October. Additional information can be found at ectc.net.

E. Jan Vardaman is president of TechSearch International (techsearchinc.com); jan@techsearchinc.com. Her column appears bimonthly.

Press Releases

- Flying Probe Testing: A Practical Solution for PCB Designs That Traditional Fixtures Cannot Test

- ubersmt Implements PARMI Xceed 3D AOI to Strengthen Inspection and Process Control

- Altus Group Expands Sales Support Function with New Appointment in Ireland

- Kitron Secures EUR 37M order for Next-Generation Tactical Communication Equipment