Organic Substrates for IC Packages: The Era Continues

Cost remains king, even as buildup substrates take hold.

In the latest issue of the Global Semiconductor Packaging Materials Outlook, organic substrate represents more than one-third of the semiconductor materials market. The main reason for this high value is the growth of flip-chip substrates, which are typically more expensive than wirebond packages.

While there has been tremendous price pressure in the packages used in the PC industry as a result of falling demand for PCs and the expansion of capacity, the growth in flip-chip CSP (FC-CSP) substrates is making up for the slower FC-PBGA dollar value growth. The expansion of FC-CSPs with laminate substrates is driven by explosive growth in mobile computing and communications devices such as smartphones and tablets. Will this growth continue? What are the future requirements for these substrates? What do the other markets for organic substrates look like? Are there opportunities in the 2.5D market for organic substrates?

Organic substrate trends. A quick look at any server or network system board shows that many of the ceramic packages of the past have been replaced by organic packages. This is not to say that ceramic packages have exited the industry, but in certain applications they have been replaced by organic packages. Intel’s shift from ceramic to laminate substrates provided a major growth driver to develop the infrastructure for organic substrates by creating high-volume demand for laminate substrates for PC microprocessors: the first packages with pin grid arrays (PGA) with pins instead of pads on the package. Microprocessors migrated to lands, remaining a socketed solution, but with the introduction of Intel’s Haswell processor for laptops, the migration from land grid array (LGA) to plastic ball grid array (PBGA) has taken off. Desktops and servers are still in LGAs.

As devices increase in complexity and features, body sizes for high-performance packages are increasing, and feature sizes are decreasing (approaching 8µm lines and spaces over the next two years). For network and servers, buildup substrates with 8-2-8 layers are in production. Intel’s latest Xeon processors

use substrates with five or six buildup layers and have a substrate size of 45 x 42.5mm. The maximum substrate size in production for network and server applications is 55 x 55mm, with projections for larger substrates in the future.

Future needs for FC-CSP substrates. Most of today’s smartphones and many tablets contain a package-on-package (PoP) where the memory is wire-bonded in the top package, and the application processor is a flip-chip in the bottom package. Other devices such as baseband processors have converted to flip-chip as well. FC-CSPs are typically 15 x 15mm or smaller. Many companies are able to design the substrate using prepreg materials and avoid use of more expensive buildup substrates, but as package roadmaps increasingly show finer bump pitch, greater use of buildup substrates is anticipated. Lines and spaces are typically 15µm (global), but features as fine as 14µm lines and spaces are found in the local area of the substrate under the die area. In the next two years, the need for 12-14µm global lines and spaces is projected, and even finer pitch will be required for local areas underneath the die. The volumes associated with mobile products continue to drive the unit volumes in the FC-CSP category, resulting in a strong market.

The future of organic interposers. At the workshop on Global Interposer Technology held at Georgia Tech in November, companies debated the future of interposers in 2.5D applications. There is a long history of silicon, ceramic and organic substrates being evaluated for use as interposers to enable die partitioning or package-level integration of different device types. There is an equally long history of laminate solutions beating out their ceramic and silicon competitors, primarily due to low cost. In the current cycle, silicon interposers have been implemented in production for the first time, starting in September 2011 for Xilinx’s partitioned FPGA application, and even earlier for Semtech’s transceiver module. The applications in production with silicon interposers remain in limited volumes, but they are high value.

Silicon interposers in production today have submicron lines and spaces, while organics are in the 10s of microns range. Organic interposers offer smaller improvements in latency and power reduction than silicon interposers do. High-performance applications could require layer counts as high as 7-2-7, and some users are questioning whether organic interposers will be able to meet cost targets. However, in terms of IR drop, organic has the advantage, and simulations have shown that organic packages are eight times better in this aspect than silicon.1 As users evaluate interposers for lower-cost applications, organic is once again under consideration. The road to 5µm or even 3µm line and space organic substrates may prove challenging, and may require different materials or process technologies. Several substrate suppliers have organic interposer capabilities in development, including Ibiden, Kinsus, Kyocera, NTK, Samsung Electro-Mechanics (SEMCO), Shinko Electric and Unimicron.

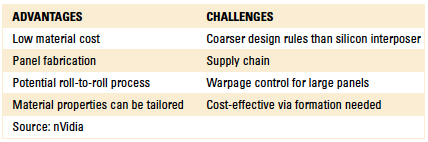

Many organizations are researching the potential of glass interposers, and several presentations at the Georgia Tech workshop provided insight into the advantages and progress with glass interposers. Glass interposers are manufactured using a fusion process that creates sheets that can be processed in a roll-to-roll format. Glass interposer thicknesses vary, but are typically 100µm, the same as silicon. The mechanical properties of glass are such that it is flexible at these thicknesses. The material properties are tailored to a CTE of 3ppm/ºC to 9ppm/ºC. Vias are formed by laser or by wet etch, and filled with copper. Table 1 shows advantages and challenges for glass interposers.

Table 1. Advantages and Challenges of Glass Interposers

At least three glass suppliers (Asahi Glass, Corning and Schott Glass) are working on via fabrication in glass, but no suppliers are ready to do RDL on glass with fab equipment, so there is no volume supplier for this solution. Many companies see potential promise for glass as a low-cost interposer solution for the future and are involved in the research at Georgia Tech, Fraunhofer, KAIST, ITRI, and other research organizations. When some of the research results from the work at Georgia Tech were presented, the workshop audience was impressed with the research in via fabrication throughput >1,000 vias per second and good reliability data for reasonably fine features on the glass substrate.

Future trends. The trend toward fine-pitch substrates in both BGAs and CSPs continues. Coreless substrates or buildup structures with four or more layers on a side have been adopted for some applications and are on the roadmaps of many companies. Substrates with finer feature sizes will be needed in the future, and the jury is still out on the choice of laminate, glass, or silicon interposers. Lower cost while meeting performance targets remains a driver for substrate development.

References

1. J. Xie, “Organic Interconnect Technology for Stacked Die Integration,” Third Annual Global Interposer Technology Workshop, November 2013.

E. Jan Vardaman is president of TechSearch International (techsearchinc.com); jan@techsearchinc.com. Her column appears bimonthly.

Press Releases

- Precision Automation & Assembly Appointed as New England Rep for Kubler US

- Precision Automation & Assembly Appointed as New England Rep for Kubler US

- AIM to Highlight NC259FPA Ultrafine No Clean Solder Paste at SMTA Rocky Mountain Expo & Tech Forum

- IDTechEx Report Unveils 3D Electronics Status and Opportunities